Noticias

Samsung utilizará transistores de nueva generación en su proceso de 3 nm

El gigante surcoreano ha confirmado que está trabajando para dar el salto a los 3 nm, un movimiento que Samsung espera completar en algún momento de 2022, y que permitirá a la compañía mantener su posición como uno de los grandes del sector de los semiconductores.

Para Samsung mantener una evolución constante en sus procesos de fabricación es fundamental, ya que la compañía no solo fabrica sus propios chips (SoCs, memoria DRAM, memoria NAND Flash, …) sino que además los ofrece a sus clientes, entre los que se encuentran nombres tan importantes como Apple, NVIDIA o AMD.

El movimiento más reciente que ha llevado a cabo Samsung ha venido marcado por el proceso de 7 nm+ (LPP, o «low power plus»), aunque la compañía surcoreana lleva un tiempo trabajando para completar la transición al proceso de 5 nm, un paso que, como en ocasiones anteriores, esperamos que tenga dos interacciones, los 5 nm LPE («low power early») y 5 nm LPP («low power plus») o 5 nm+.

Cuando se complete esa transición dará comienzo la carrera hacia los 3 nm, un desafío importante que obligará a Samsung a utilizar transistores de nueva generación para que este sea viable. Esto tiene una explicación, y es que con cada reducción de proceso disminuye el grosor de las puertas lógicas en los semiconductores, lo que puede derivar en una debilidad estructural que propicie las fugas eléctricas y que impida el correcto funcionamiento de los transistores.

Ahora que tenemos eso claro estamos preparados para entender a la perfección por qué hemos dicho que Samsung necesita utilizar transistores de nueva generación: porque solo con ellos es capaz de controlar el tema de las fugas eléctricas derivadas de la reducción de procesos de fabricación.

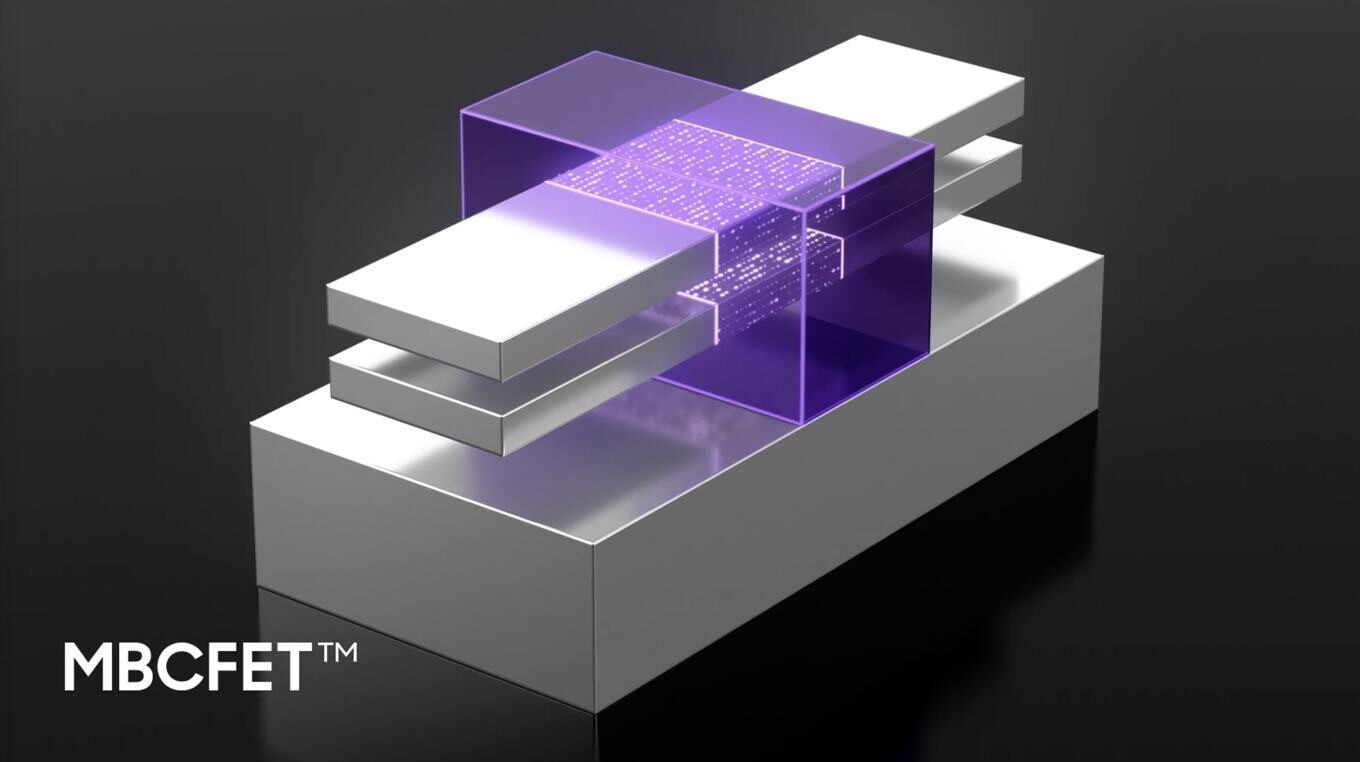

En este caso en concreto la firma surcoreana utilizará transistores «Gate-All-Around FET», que permitirán disponer de un control mejorado del canal de los transistores y facilitará la prevención de fugas eléctricas incluso en nodos de pequeño tamaño. Estos transistores se combinarán con la tecnología «Multi Bridge Channel FET», que permitirá reducir el consumo hasta en un 50% y aumentar el rendimiento hasta en un 30%.

Son valores muy buenos, de eso no hay duda. Samsung no ha concretado qué aumento de la densidad de transistores podemos esperar, pero por la reducción que se producirá al saltar a los 3 nm debería rondar entre el 45% y el 50%.

-

OpiniónHace 6 días

OpiniónHace 6 días10 predicciones para los proveedores de servicios gestionados en 2025

-

NoticiasHace 6 días

NoticiasHace 6 díasAMD despedirá al 4% de su plantilla mientras se centra en IA y centros de datos

-

NoticiasHace 2 días

NoticiasHace 2 díasEl Capitan es el nuevo superordenador más potente y rápido del mundo

-

NoticiasHace 6 días

NoticiasHace 6 díasLa Comisión Europea multa a Meta con 798 millones por perjudicar a la competencia de Marketplace