Noticias

Intel repasa sus avances en el escalado de transistores y sus próximos nodos

Durante la celebración del IEDM 2023 Intel ha aprovechado para repasar sus avances en el escalado de transistores y en la fabricación de semiconductores. En este sentido una de las novedades más interesantes fue la presentación de sus avances en transistores CMOS (semiconductores complementarios de óxido metálico) apilados en 3D, combinados con alimentación trasera y contactos traseros directos.

Sanjay Natarajan, Intel vicepresidente senior y director general de Investigación de Componentes, comentó que:

«A medida que nos adentramos en la Era Angstrom y miramos más allá de los cinco nodos en cuatro años, la innovación continua es más crítica que nunca. En IEDM 2023, Intel muestra su progreso con avances en investigación que alimentan la Ley de Moore, subrayando nuestra capacidad para aportar tecnologías punteras que permitan un mayor escalado y un suministro eficiente de energía para la próxima generación de informática móvil.”

Esto es muy importante porque el escalado de transistores y la reducción de los nodos de fabricación son fundamentales para cubrir las necesidades de semiconductores más potentes y eficientes. La reducción del tamaño de los transistores juega un papel fundamental en este sentido, pero también tenemos otros frentes que son clave, como el apilado de transistores.

Anuncios y novedades de Intel

Primeros transistores CMOS apilados en 3D combinados con alimentación y contacto trasero:

-

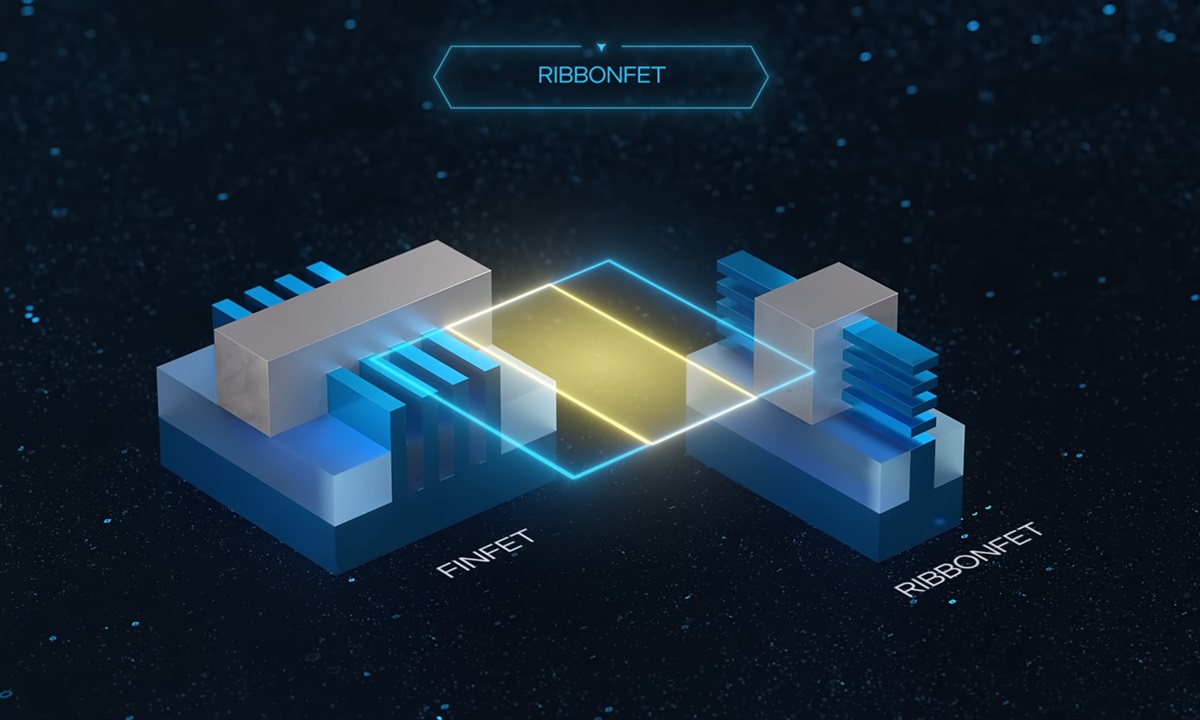

Las últimas investigaciones sobre transistores de Intel presentadas en IEDM 2023 muestran una primicia en el sector: la capacidad de apilar verticalmente transistores de efecto de campo complementarios (CFET) con un paso de puerta escalado hasta 60 nanómetros (nm). El apilamiento de transistores permite aumentar la eficiencia y el rendimiento. También se combina con alimentación y contactos traseros directos. Esto demuestra la capacidad de la empresa para innovar más allá de los transistores RibbonFET.

Intel va más allá de los cinco nodos en cuatro años e identifica las áreas clave de I+D necesarias para continuar con el escalado de transistores con suministro de energía trasera:

-

PowerVia de Intel estará lista para fabricación en 2024, lo que supondrá una de las primeras implementaciones de la entrega de energía trasera. En IEDM 2023, el grupo de Investigación de Componentes identificó vías para ampliar y escalar la entrega de energía trasera más allá de PowerVia, así como los avances clave en los procesos necesarios para hacerlos posibles. Además, este trabajo también puso de relieve el uso de contactos traseros y otras interconexiones verticales novedosas para permitir el apilamiento de dispositivos con eficiencia de área.

El gigante del chip es el primero en integrar con éxito transistores de silicio con transistores de GaN en la misma oblea de 300 mm y demostrar que funciona bien:

-

En IEDM 2022, Intel se centró en las mejoras de rendimiento y en la creación de una ruta viable hacia las obleas de GaN en silicio de 300 mm. Este año, la empresa está avanzando en la integración de los procesos de silicio y GaN. Intel ha demostrado con éxito una solución de circuito integrado de alto rendimiento a gran escala, denominada «DrGaN», para el suministro de energía. Los investigadores de Intel son los primeros en demostrar el rendimiento de esta tecnología y su potencial para ofrecer soluciones de suministro de energía que satisfagan los requisitos de densidad y eficiencia energética de la informática del futuro.

Intel avanza en I+D en el espacio de los transistores 2D para el futuro escalado de la Ley de Moore:

-

Los materiales de canal 2D de dicalcogenuros de metales de transición (TMD) ofrecen una oportunidad única para escalar la longitud física de la puerta de los transistores por debajo de los 10 nm. En IEDM 2023, Intel demostrará prototipos de transistores TMD de alta movilidad para NMOS (semiconductor de óxido metálico de canal n) y PMOS (semiconductor de óxido metálico de canal p), los componentes clave de CMOS. Intel también presentará el primer transistor TMD PMOS 2D con puerta de acceso perimetral (GAA) del mundo y el primer transistor PMOS 2D fabricado en una oblea de 300 mm.

-

OpiniónHace 6 días

OpiniónHace 6 días10 predicciones para los proveedores de servicios gestionados en 2025

-

NoticiasHace 7 días

NoticiasHace 7 díasAMD despedirá al 4% de su plantilla mientras se centra en IA y centros de datos

-

NoticiasHace 3 días

NoticiasHace 3 díasEl Capitan es el nuevo superordenador más potente y rápido del mundo

-

NoticiasHace 7 días

NoticiasHace 7 díasLa Comisión Europea multa a Meta con 798 millones por perjudicar a la competencia de Marketplace